Today’s heterogeneous integrated semiconductor packages are breakthroughs that enable dramatic increases in bandwidth and performance while reducing power consumption and cost compared to what is currently achievable with traditional monolithic SoC designs. It’s technology.

Figure 1. Heterogeneous integration device with 47 chiplets. (Image source: Intel)

The evolving packaging design landscape requires designers and design teams to adapt to a new and dynamic set of best practices, techniques, processes, and methodologies. Adopting these new approaches is essential to creating packaging that not only appeals to consumers, but also responds to the evolving demands of sustainability, technology, and consumer preferences.

By staying at the forefront of these innovations, designers can ensure that their work is not only visually appealing, but also functionally efficient and environmentally responsible, ensuring that the final can contribute to a more successful and sustainable future in the field of packaging design.

To effectively design these new types of packages, designers and design teams must adopt a new set of best practice design techniques, processes, and methodologies.

These best practices are defined as follows:

- Achieve board supplier manufacturing requirements

- Shift Left “Big Rock” Power Supply Analysis

- Employs efficient high-bandwidth memory (HBM) integration techniques

- Leverage simultaneous team design

- Leverage physical design IP reuse

- Efficiently design daisy chain test vehicles

- Use data path planning and routing

Meeting board supplier manufacturing requirements

Packaging manufacturers have strict metal fill requirements that address two major issues. First, the dielectric and metal layers are very thin, less than 15 µm, so pockets of trapped gas can cause delamination during the build-up and redistribution layer creation process. Second, uneven conductor density on the same layer or between layer pairs can cause package or wafer warpage. As a result, board manufacturers do not prefer solid metal surfaces or large metal areas.

To avoid these problems, rules, design rule checks, and often design rule manuals are typically provided. All of these issues and rules combine to make the designer’s job of meeting manufacturer acceptance criteria difficult. Additionally, the diversity of board technologies from numerous vendors means there is no one-size-fits-all solution.

There are three methodologies that designers typically use to mitigate or control these issues.

- Hatched filled metal area with layer offset

- Outgas void pattern insertion

- Dummy metal fill insertion

Xpedition Package Designer has proven automation capabilities for all three methodologies. Understand how to use these features efficiently and effectively to avoid extended design cycles and ECOs due to manufacturer rejection of designs.

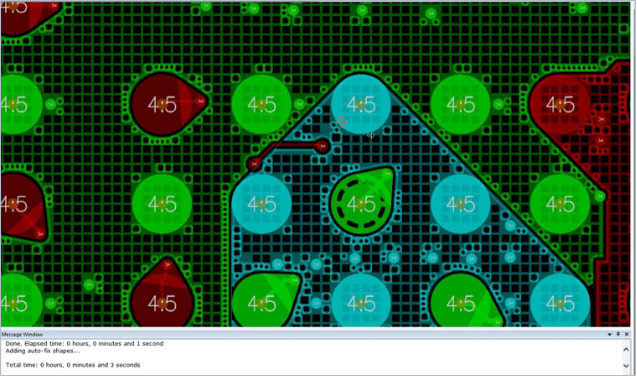

Figure 2. Hatched copper fill with additional automatic deaerator and wagon wheel pad.

Shift Left “Big Rock” Power Supply Analysis

Today, power requirements continue to increase as more dies (or chiplets) are added to packages. The ability to analyze the power characteristics of the core and understand whether there are enough vias and copper to meet the current requirements of the IC is critical to success. When multiple dies are integrated into a high-density, heterogeneous package, not only do they need to be powered through multiple rails, but the current supply path is also complicated because the multiple dies that draw current from the rails are in different locations. complexity increases.

Additionally, there is less space for connecting power supply voltages and currents to the die than in a single monolithic package. With this increase in density, there may not be enough copper to meet the design requirements of all the chiplets, and as a result, there may not be enough copper in the package just to support the current requirements of all these different dies. may require additional layers.

The recommended approach is to identify large DC drop problems (rocks) early to improve the final result. This procedure is not focused on pursuing the highest level of accuracy for signoff purposes. The “big lock” approach essentially allows designers to identify potential problems as early as possible that would not otherwise be discovered, thereby avoiding costly changes and delays. Designers start by obtaining very basic information about the die or components included in the design.

Once the package designer has the basic information, Siemens Xpedition Package Designer software (xPD) makes it easy to enter voltage rail current values, all from within the tool. Analysis results from Siemens HyperLynx software are automatically annotated into xPD, allowing users to clearly see violations in specific locations. Designers can click on an error, automatically zoom to the problem area, fix it, and rerun the analysis.

HBM integration methodology

HBM is de facto Although standard for high-performance computing applications such as CPUs, GPUs, and AI, the 1,024-bit bus is divided into either 8 x 128-bit or 16 x channels, making it difficult to route in an efficient manner. It Is difficult. 64 bit.

The challenges for packaging designers fall into four broad areas.

- Maintaining signal integrity

- Strengthening the stability of power supply

- Ensure enough real estate for routing

- Ensuring sufficient design cycle time to implement HBM bus channels within specification

Creating composite via geometry for fanout and breakout structures is the first step in channel implementation. Following this, the bits of the channel are routed from the complex through the logic die side breakouts to the breakouts on his HBM stack. Once this first channel is completed and electrical compatibility is characterized, it can be considered good and ready for replication and reuse.

Meanwhile, improvements to computing chiplets (SoCs) often impact die bumps and pin assignments. If some of the existing replicated channels are modified and the changes need to be propagated to other channels, a time-consuming ECO will occur unless intelligent circuit replication is used. That’s where PhRC can help. PhRC offers a total time savings of 25% compared to traditional cut, copy, and paste, and up to 75% when combined with automated ECO.

Figure 3. A complete HBM bus as a PhRC that can be intelligently replicated.

simultaneous team design

There’s an old saying that goes, “Many hands make a simple job,” and this is especially true when designing package substrates. Modern heterogeneous packaging can be significant in size, content, and complexity, so ensure that your design complies with manufacturing and assembly rules, and that your process to meet PPA and cost objectives is It has become very difficult for a single designer.

Historically, this challenge has been solved using design changes. This is especially useful for companies with geographically dispersed teams. In theory, three different designers could each work her 8-hour shift and design continuously around the clock. But while this is a good thing and may work for some companies, it can only apply her one designer’s expertise at a time. And you can’t expect one designer to be a master of everything.

Fortunately, with concurrent team design, no one has to do that. Imagine three to five different design domain experts working simultaneously in real time, each focused on a specific design challenge that aligns with their expertise. Each designer can see what the other designers are doing and can even set floor plan restriction areas to notify other designers not to focus on those areas. The result is a design environment that can double engineering resources and involve experts at the same time. The result is shorter design cycles, higher design quality, and faster time-to-volume production.

Physical design IP reuse

Cut, copy, and paste are often thought of as physical design IP reuse, and while this is true at the most basic level, it has significant limitations. Although acceptable in some situations, it is unacceptable in most cases because it is error-prone, requires manual netlist manipulation, and lacks traceability to the golden source data.

Most package designs include areas of symmetry that are ideal for reuse, such as die-to-die wiring for standard interfaces, core power and ground supply structures with complex via arrays, and device fanouts. These Physical Design Reuse Circuits (PhRC) provide dynamic net propagation from the parent netlist, enable rapid ECO, and manage a golden source of verified design content using native, first-class design object. PhRC promotes design modularity, requires no netlist changes, and provides a non-invasive ECO process. They are built using validated content, and their placement can be used across designs, designers, and teams.

Figure 4. Eight PhRC blocks with reusable fanout routing.

Efficient design of daisy chain test vehicles

Semiconductor package test vehicles are commonly referred to as daisy-chain designs due to their heavy use of daisy-chain metal wiring. The test vehicle has the physical characteristics (e.g. number of layers) of the actual target design and uses the same parts. Daisy chain wiring on test vehicles is used to test mechanical connections such as CTE and solderability. The physical structure, including materials, processes, and design features, are then tested.

Finally, copper structures such as heaters, serpentine vias, and offset vias are tested. Creating and visualizing a test vehicle design can be very time consuming. By working closely with many customers, Siemens

The Daisy Chain Creator toolkit allows you to select chains across die, package, and PCB interfaces. This allows you to easily color and name your chain. It also enables the creation of documentation for the engineers performing the tests.

Data path planning and routing

Previous packages were simply point-to-point reroute connections between the die, microbumps, and the package’s BGA. There were some differential pairs, but overall it was primarily a matter of “connecting the dots.”

With the advent of heterogeneously integrated chiplets, the situation has changed. Chiplets themselves are functionally fragmented versions of what was once a monolithic SoC. A large amount of data is exchanged between these chiplets, much of it at very high speeds using complex data bus protocols. Packages are now system interconnect platforms that enable the collection of computing chiplets and associated memory to meet the intended goals of device architects.

Connectivity is no longer just about “connecting the dots.” One reason for this is that there is a wide range of data buses such as his HBM and other protocols that connect computing chiplets. Datapath planning is done during package floorplanning because chiplet placement depends on interconnect datapaths to other chiplets and external package pins. A designer can group interfaces or byte lanes into bundles and floorplan them to evaluate root real estate and chiplet breakout strategies. Once these datapath plans are determined to be viable scenarios, they can be annotated and transferred to the actual physical design for detailed implementation.

Figure 5. Datapath planning and wiring.

conclusion

To learn more about the challenges and benefits of exciting IC packaging technology and seven best practices for physical design of IC packages, check out Siemens EDA’s new eBook, Best Practices for Physical Design of IC Packages.